Cadence dan TSMC telah lama bekerja sama dalam membangun infrastruktur desain untuk node proses lanjutan, termasuk N3, N2, dan A16, dengan dukungan penuh dari rangkaian solusi EDA Cadence seperti Innovus Implementation System, Tempus Timing Solution, hingga Virtuoso Studio. Kini, alur desain berbasis AI dari Cadence juga tersedia untuk teknologi 3DFabric milik TSMC, yang memungkinkan integrasi chiplet dan kemasan 3D lebih efisien.

Selain itu, kedua perusahaan tengah mengembangkan alur EDA untuk proses A14, dengan process design kit (PDK) pertama dijadwalkan rilis akhir tahun ini. Beberapa IP terbaru Cadence juga telah terbukti di silikon dan siap digunakan pada node N3P, termasuk memori berkecepatan tinggi dan antarmuka konektivitas generasi baru.

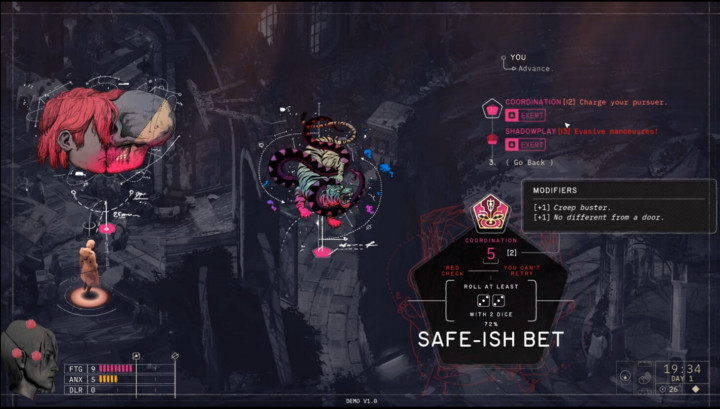

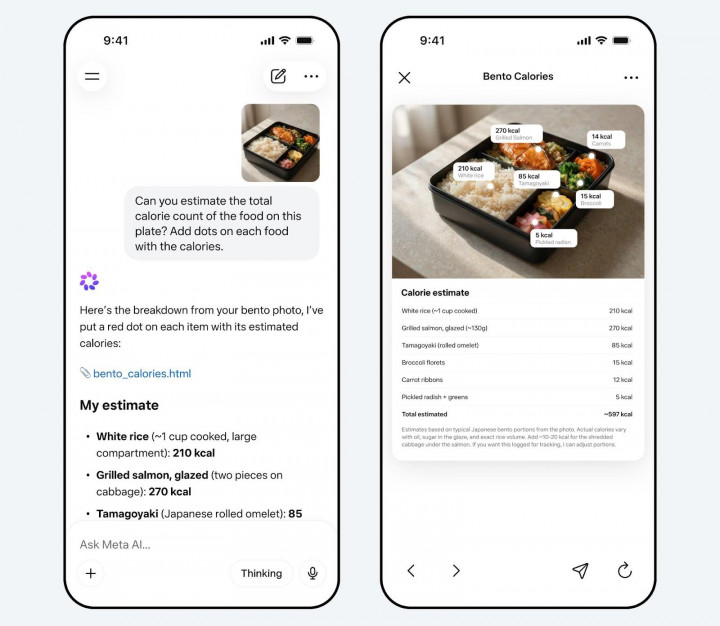

Dalam ranah AI, TSMC telah mengintegrasikan solusi Cadence JedAI dan Cerebrus Intelligent Chip Explorer ke dalam alur desain digitalnya. Fitur berbasis AI ini mencakup otomatisasi perbaikan pelanggaran design rule check (DRC), yang mempercepat proses penutupan desain sekaligus meningkatkan efisiensi daya, performa, dan area (PPA).

Untuk desain 3D-IC, Cadence menghadirkan otomatisasi koneksi bump, penyelarasan chiplet, serta analisis signal integrity dan power integrity berbasis AI. Dukungan ini diperkuat dengan simulasi termal canggih yang memastikan kinerja fotonik dan elektrik tetap stabil pada sistem berskala besar.

Di sisi IP, Cadence memperkenalkan HBM4 pertama di N3P, antarmuka memori LPDDR6/5X hingga 14,4 Gbps, serta DDR5 MRDIMM Gen 2 pada 12,8 Gbps. Untuk konektivitas, tersedia PCIe 7.0 (128 GT/s), 224G SerDes, hingga UCIe 32G, yang dirancang untuk mengatasi “memory wall” pada sistem AI modern.

Menurut Cadence, kolaborasi ini bertujuan mempercepat perjalanan pelanggan dari desain hingga silikon, sekaligus mendukung infrastruktur AI yang lebih hemat energi dan dapat diskalakan. TSMC menegaskan bahwa kemitraan melalui ekosistem Open Innovation Platform (OIP) akan menjadi kunci dalam mendorong “AI supercycle” global.

Cek Berita dan Artikel yang lain di

Google News